|

|

|

|

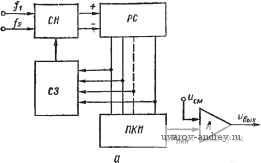

Главная страница » Электрика в театре » Схемы с частотным преобразованием 1 ... 4 5 6 7 8 9 10 ... 16 Генератор, выполненный по схеме рис. 8, б, вырабатывает высокостабильную последовательность импульсов /ц. Частота управления PC вырабатывается управляемым генератором частоты УГЧ. Частота уставки ускорения fy изменяется напряжением Ну, при этом изменяется ускорение (замедление) двигателя. Для ручной коррекции задания используются импульсы низкой частоты (около 0,5 Гц), вырабатываемые низкочастотным генератором НГ. Схема ввода и хранения кода задания служит для ввода кода задания и записи его в регистр памяти. В ее состав входят три многопозиционных переключателя П типа ПМП-105 и регистр задания РЗ. В состав переключателей входит дешифратор десятичного кода в двоично-десятичный код 8-4-2-1. Частотно-задающее устройство работает следующим образом. В исходном состоянии PC обнулен, выходная частота на выходе ЧЗУ отсутствует. Переключатели устанавливаются в положения, соответствующие десятичным цифрам вводимого числа, при этом с выходных клемм переключателей вводимое число в двоично-десятичном коде 8-4-2-1 поступает на вход регистра задания РЗ. При нажатии кнопки Работа этот код записывается в РЗ, и ССК вырабатывает сигнал Л > В (где А - код задания, В - код PC). При этом импульсы частоты fy начинают поступать на счетный вход PC. С каждым импульсом частоты fy код PC изменяется на единицу, что приводит к изменению выходной частоты вращения на I мин-. При достижении заданной частоты вращения, когда код в PC равен коду, хранящемуся в РЗ, ССК вырабатывает сигнал А = В, который поступает в СФК- Действие команды Работа прекращается. Импульсы частоты не поступают. В этом режиме PC выполняет роль оперативной памяти, где хранится код числа, соответствующего заданной частоте вращения. При необходимости изменения частоты вращения в регистр задания РЗ при помощи переключателей вводится новое число, при этом на выходе ССК появ- ляется сигнал А Ф В {А:> В или А < В), который управляет соответственно шиной сложения или вычитания PC. Изменение скорости производится после нажатия кнопки Работа. Для полного останова двигателя вьщается команда Стоп. При этом регистр сбрасывается в нуль и вССК поступает нулевое значение кода. Сигнал Л < В с выхода ССК поступает на управление вычитающей шиной PC. Одновременно импульсы частоты управления /у поступают на вход PC, уменьшая содержимое счетчика до нуля. При выдаче команды Так держать в процессе разгона или торможения вход PC блокируется и выходная частота определяется кодом, который записан в PC к моменту выдачи команды. Режим ручной коррекции частоты вращения двигателя производится подачей команд Больше и Меньше. При этом .импульсы с выхода низкочастотного генератора НГ поступают на счетный вход PC, соответственно на сложение или вычитание. Одновременно блокируется выход ССК, так как под действием сигналов ССК устройство будет стремиться вернуться в первоначальное состояние. Благодаря низкой частоте импульсов коррекции можно контролировать изменение скорости визуально и уменьшать ошибки оператора. Для уменьшения неравномерности выходных импульсов УДЧ на выходе устройства включен буферной делитель БДЧ, который представляет собой пятиразрядный двоичный счетчик. Выходная частота контролируется с помощью узла цифровой индикации ЦИ. При работе с тахогеиератором ТТ-245-1П в качестве частотного датчика обратной связи, который выдает 552 импульса за 1 мин-, частота кварцевого генератор а/о =552х ХПмакскБДч/О, где Пмакс = ЮОО МИН - мзксимальная задаваемая частота вращения; квдч = 32 - коэффициент деления БДЧ. Стабильность частоты составляет 0,5-10 , диапазон выходной частоты 9,2 Гц...9,2 кГц с дискретностью 9,2 Гц, что соответствует изменению задания от 1 до 1000 мин- с дискретностью в 1 мин-. Глава третья ФУНКЦИОНАЛЬНЫЕ УЗЛЫ ЦИФРОАНАЛОГОВЫХ САУ С ЧACTOTHЫiV]И СИГНАЛАМИ 1. ЦИФРОВЫЕ ИНТЕГРАТОРЫ Цифровой интегратор на базе реверсивного счетчика. Упрощенная схема такого интегратора показана на рис. 19. Основой его является реверсивный счетчик PC числа импульсов, на суммирующий вход которого поступают импульсы частоты /i, на вычитающий - f. Схема несовпадений СН как бы раздвигает импульсы fi и /а во времени, если моменты их прихода совпадают (или близки), и тем самым обеспечивает четкую работу PC. Таким образом, в каждый момент времени в счетчике записано число, равное разности между числом периодов частот /i и /г от момента начала работы счетчика. Схема защиты СЗ предотвращает опрокидывание счетчика при переполнении или обнулении. На выходе счетчика устанавливается преобразователь код - напряжение ПКН. Если интеграл от разности частот может принимать как положительные, так и отрицательные значения, то необходимо принять специальные меры для получения двухполярного напряжения на выходе ПКН. Например, при включении счетчика можно записсть в него некоторое число, а получающееся при этом выходное напряжение ПКН скомпенсировать на выходном усилителе схемы с помощью смещения. Если интеграл от разности частот примет  I I \ I I I I I H D П П П П Рис. 19. Структурная схема (a) и временные диаграммы (б) цифрового интегратора на базе реверсивного счетчика отрицательное значение, в счетчике будет записано число, меньшее начально установленного, а выходное напряжение усилителя А станет отрицательным. Если пренебречь явлениями квантования, то uit)K{h-f2)dt, (8) о где К - изменение напряжения на выходе ПКН при изменении содержимого счетчика на единицу. Рассмотрим работу такого интегратора подробнее На рис. 19, б показано выходное напряжение ПКН при раз- ГТИ личных fi и /г- Участки 1 к 2 соответствуют = при разных временных сдвигах между моментами прихода импульсов /] и /г- Среднее значение выходного напряжения пропорционально сдвигу. Это напряжение может принимать любую величину (хотя амплитуда и принимает только квантованные значения NcyK), в связи с чем при использовании описываемого интегратора отсутствуют автоколебания, вызываемые квантованием по уровню. В то же время на выходе системы возникают колебания, вызванные ступенчатым изменением и (t). Определим точность выполнения операции интегрирования в цифровом интеграторе. Предположим, что частота постоянна, а частота h=f2 + h sin (©0+ Фо). т. е. изменяется по синусоидальному закону. Таким образом, период Та = I 2 (промежуток времени между приходами соседних импульсов) постоянен, а f-й период частоты определяется уравнением [16] ± ссг счг о J \и + /о sin Ы + tOo + Фо)] = 1 Для заданных значений f, / , ©о. Фо можно из выражения (9) последовательно определить Г^, Tj, Ti и построить процесс и (t). При этом должно выполняться условие периодичности Т^/Т -ш, где Та =2п/щ, т - целое число. После построения и (t) на отрезке времени Гщ эту функцию можно разложить в ряд Фурье и найти амплитуду Рис. 20. Структурная схема цифроаналогово-го интегратора АI и фазовый сдвиг первой Ф1 и высших гармоник разложения и затем сравнить и ф| с амплитудой и фазовым сдвигом на выходе идеального интегратора. Фазовый сдвиг на выходе такого интегратора равен - я/2, а амплитуда Л„ = foK/щ == !оКТт/2л и не зависит от фо- Из проведенных с помощью ЦВМ расчетов видно, что при m = 2 наблюдается сильная зависи- DmCvf ссз 1 [ к триггеру Рис. 21. Структурная схема защиты мость Л^ И Ф1 от Фо, а при т = и выше Л, = Л„ И Ф1 = -п/2. Таким образом, если полоса пропускания системы регулирования составляет менее 1/4 минимальной частоты задания (или обратной связи), то цифровой интегратор можно рассматривать как непрерывный. Цифроаналоговый интегратор с широтной модуляцией. Недостатком описанного выше инте-граторана базе реверсивного счетчика является необходимость в двухполярном преобразователе код -напряжение, являющимся достаточно сложным устройством. Отличительной особенностью интегратора с широтной модуляцией является промежуточное преобразование разности числа импульсов в широтно-модулированный сигнал, скважность которого пропорциональна интегралу от разности частот [15, 29, 30]. Структурная схема интегратора показана на рис. 20. Генератор тактовых импульсов ГТИ вырабатывает две последовательности коротких импульсов одинаковой частоты Fi и Fi, сдвинутых по фазе на 180°. Импульсы частоты за- дания и обратной связи с помощью схем синхронизации вводятся в соответствующие счетчики синхронно с тактовой частотой Fa- Частота Fi используется для заполнения счетчиков Сч1 и Сч2, работающих в режиме деления частоты, с целью образования широтно-импульсно-модулированного (ШИМ) сигнала на выходе триггера управления Т с коэффициентом заполнения К = 0,5 при отсутствии частот Д й fa- Схема защиты предотвращает изменение фазы ШИМ сигнала на 180° при переполнении одного из счетчиков в случае больших рассогласований и сохраняет знак выходного напряжения демодулятора ДМ, обеспечивающего преобразование ШИМ сигнала в напряжение постоянного тока. Структура схемы защиты показана на рис. 21. Входные логические схемы ЛС1 и ЛС2 в нормальном режиме работы интегратора пропускают импульсы переполнения счетчиков, поступающие поочередно на входы схем синхронизации ССЗ и СС4, выходные импульсы которых управляют работой сдвигового регистра PC, причем импульсы с выхода ССЗ продвигают единицу в реверсивном регистре слева направо, а импульсы с выхода СС4 - в обратном направлении. При этом обеспечивается нормальное переключение триггера управления. Режим защиты наступает, когда один из счетчиков переполнится 2 раза и более, а другой не успеет переполниться за этот же отрезок времени. При этом происходит запись единицы в один из крайних разрядов реверсивного регистра и выходные импульсы последнего будут воздействовать только на один вход выходного RS-триггера, режим переключений которого прекращается. Количество импульсов переполнения, при котором обеспечивается режим запоминания определяется емкостью реверсивного регистра. В режиме, когда емкость динамической памяти будет исчерпана, наступит режим запрета поступления импульсов на реверсивный регистр, который обеспечивается схемой блокировки и логическими схемами. Особенностью данной схемы защиты является наличие реверсивного сдвигового регистра, представляющего собой оперативную память и позволяющего судить о количественной разности частот fi и / g при больших рассогласованиях. Емкость динамической памяти должна быть выбрана такой, чтобы она не исчерпывалась при максимально возможной величине интеграла от рассогласования. В тех случаях, когда в САУ вырабатывается пропорциональная составляющая ошибки, целесообразно включать интегратор только при небольших величинах рассогласования, соответствующих точности работы пропорциональной составляющей. Для количественного описания статических и динамических характеристик цифроаналогового интегратора введем следующие обозначения: = l/F-it = IjF- - период тактовой частоты, принимаемый за единицу измерения времени; Ti и - периоды частот и /j; Т - период переключения выходного триггера; 4 - длительность единичного уровня напряжения выходного триггера; - длительность нулевого уровня напряжения выходного триггера; К = 2 - емкость двоичного счетчика; п - число разрядов двоичных счетчиков; k = tJT - коэффициент заполнения ШИМ колебаний. При Д =: / з = О на входы счетчиков поступают импульсы только тактовой частоты Ftj. Значение коэффициента заполнения зависит от начального состояния счетчиков. Примем, что в исходном состоянии в старшем разряде одного счетчика записана единица, а во втором счетчике - все нули. Тогда импульсы переполнения счетчиков будут сдвинуты во времени на половину периода их следования, т. е. t = 0,57; k = 0,5; Т = Среднее значение напряжения на выходе демодулятора равно нулю, если напряжения единичного и нулевого уровней разнополярны. Пусть = 0. Обозначим b = Т^/Т^, тогда период ШИМ сигнала Т уменьшится. Действительно, за время t на счетчик поступит число импульсов = t/T., + t/Ti == = t{T+ Ti)l{T,Ti) = / (1 + следовательно, вели- чина среднего периода колебаний выходного триггера Гер = VT,bl( 1 + 6) = Тф1{\ + Ь), (10) где 0 - период колебаний триггера при f-y =f = 0. Действительная величина каждого периода кратна целым числам периодов Т^, поэтому период переключения может быть равен целой части Vbl{\ + b) или целой части ybli} + b) +1. Если, например, F= =64, b = 10, то величины периодов T/TV =58 и Т'IT. =59. Порядок пере- Таблица 2

ключения триггера, т. е. порядок следования импульсов с периодами Т' и Т зависит от соотношения частот Д (/2) hFti, а также емкости счетчика Через определенный промежуток времени - период неравномерности Т„, порядок следования импульсов на выходе триггера повторится. Это осуществляется при выполнении условия: КЛ/ = n,(l + 1/Ь), (11) гдеЛц - число колебаний триггера за время Т^, а -число импульсов тактовой частоты, причем Nnn - наименьшие целые числа, при которых выполняется условие (11). Если 2 Ь/(1 + Ь) = bi - целое число, то период Т'н= bjX 7]j =; const. В табл. 2 приведены зависимости N,n их TJT от Ь при V = 256. Могут быть случаи, когда на каком-то такте переполнение счетчика вызывается импульсом fi или f. Эти импульсы сдвинуты на 0,57 по отношению к Fti, поэтому появляются периоды, кратные 0,57, что усложняет картину. В результате коэффициент заполнения на каждом периоде колебаний триггера может отличаться от 0,5, однако при усреднении за время Т„ k = 0,5. Этот вьшод относится к тому случаю, когда импульсы fi и fa поступают в один и тот же момент времени. Для интегратора на реверсивном счетчике при Д = /2 среднее выходное напряжение пропорционально временному сдвигу между этими последовательностями (т. е. фазовому сдвигу между ними). С помощью ЦВМ были проведены расчеты, заключающиеся в построении кривой напряжения на выходе триггера при различных фазовых сдвигах между fi и и нахождении среднего значения вых. В результате найдено, что если за время усреднения принять время неравномерности, то среднее значение выходного напряжения интегратора пропорционально фазовому сдвигу (за исключением случаев, когда 2 Ь/(1 + Ь) - целое), причем вь = oA/(0,5KTi), (12) где А - временной сдвиг между последовательностями Д и h, о - напряжение питания триггера (точнее, напряжение единичного уровня на выходе триггера). Пусть fi Ф /2, причем и /2 постоянны. Тогда начинается процесс интегрирования разности количества импульсов, поступающих на входы интегратора; изменение выходного напряжения при поступлении одного импульса или /j Мвь,х = А:д„Ыо/2 ~, (13) где йдм - коэффициент передачи демодулятора. Интегратор накапливает все предыдущие отклонения между количеством импульсов и /2, усредняя их во времени за период колебаний ШИМ сигнала. Изменение отрезка времени, в течение которого триггер находится в определенном положении, после каждого переброса в противоположное состояние одинаково и определяется как разность [см. уравнение (10)]: AT = Т, (bi -б2)/(1 + М (1 + Ь.). (И) 1 ... 4 5 6 7 8 9 10 ... 16 |

|

© 2000-2026. Поддержка сайта: +7 495 7950139 добавочный 133270.

Заимствование текстов разрешено при условии цитирования. |