|

|

|

|

Главная страница » Электрика в театре » Схемы с частотным преобразованием 1 ... 3 4 5 6 7 8 9 ... 16 ползучей скорости, когда Таблица I Выходы схем И каждой группы через элементы 15 и je схемы ИЛИ соединены с входами триггера управления. Q помощью такой схемы можно определять направление вращения в режимах остановки отсутствует сигнал задатчика направления. В режиме реверса природа схема работает следующим образом. С поступлением команды на реверс сигнал логической единицы появится на противоположном выходе задатчика направления. На выходе соответствующей четырехвхо-довой схемы И появится сигнал логической единицы только в момент, когда частота вращения достигнет нулевого значения и на выходах всех фазных формирователей установятся логические единицы. Этот сиг-нал,воздействуя через схему ИЛИ на триггер управления, изменяет его состояние, что приводит к изменению полярности выходного сигнала датчика. С нача-

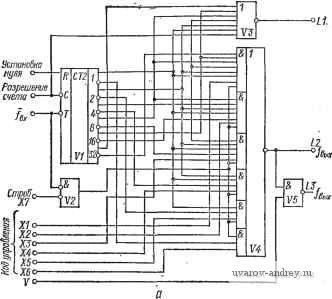

Примечания: I. Амплитуда линейного напряжения 0...200 В. 2. Номинальная мощность 25 Вт, нелинейность выходной характеристики 1%, напряжение возбуждения 60 В. 3. Рабочий диапазон температур -10...-Ь50° С. ЛОМ вращения в другую сторону вступает в работу вспомогательный канал, и дальнейшая работа схемы протекает так же, как в режиме разгона. С помощью вспомогательного канала определения направления вращения выделяются импульсы данного направления вращения, которые, поступая через схему ИЛИ на вход триггера управления, подтверждают его состояние. Тахогенераторы переменного тока являются одновременно амплитудными и частотными датчиками. Это их существенное преимущество по сравнению с другими датчиками частоты вращения. Основные технические данные тахогенераторов типа ТТ приведены в табл. 1. Приведенные выше датчики частоты вращения могут использоваться и как датчики положения, если одному периоду квантования частоты будет соответствовать единица измеряемой величины, а количество периодов будет под-считываться и фиксироваться. При этом емкость счетчика и регистра памяти должна быть достаточная для измерения полного перемещения. Другой вид частотных датчиков положения также относится к электромагнитным по физической системе, но по механизму действия уже принадлежит к частотно-зависимым системам. Эти датчики выполняются на основе управляемых LC-, LR- и 7?С-генераторов, в которых изменение индуктивности L, емкости С или сопротивления R приводит к изменению частоты и позволяет получить зависимость между положением объекта и частотой выходного сигнала. Наиболее распространены датчики, основанные на LC- и Li-генераторах, в которых осуществляется изменение индуктивности L контура за счет перемещения сердечника катушки, кинематически связанного с объектом измерения [9, 20]. В датчиках, основанных на 7?С-генераторах, частота изменяется при изменении емкости С конденсатора, одна из обкладок которого механически соединяется с измеряемым объектом [22 ]. Температурную нестабильность компенсируют, используя термосопротивления в цепях, определяющих частоту генератора, или применяют балансные схемы. Существуют другие частотные датчики регулируемых величин, многие из которых используются в цифроаналоговых системах управления, описанных в работах [2, 8, 9, 20, 22]. 2. ЧАСТОТНЫЕ ЗАДАЮЩИЕ УСТРОЙСТВА Одним из основных способов задания регулируемой величины в цифроаналоговых системах управления является частотный, т. е. с помощью частотных задающих устройств (ЧЗУ) формируется последовательность импульсов, частота или период следования которых пропорциональны задаваемому значению регулируемого параметра. Высокая стабильность частоты достигается за счет применения кварцевых генераторов. По принципу формирования импульсной последовательности ЧЗУ можно разделить на две группы: 1) обеспечивающие линейную зависимость между уставками задающего кода и выходной частотой следования импульсов; 2) обеспечивающие линейную зависимость между задающим кодом и периодом следования выходных импульсов. Преимущественно используются ЧЗУ первой группы, так как большинство цифровых регуляторов работает по принципу сравнения частот задания и обратной связи. Основным функциональным узлом такого ЧЗУ является управляемый делитель частоты (УДЧ). Различают двоичные и двоично-десятичные УДЧ. Двоичные имеют более простую структуру, однако ввод коэффициентов деления в них должен производиться в двоичном коде, что усложняет схему. Отечественная промышленность выпускает интегральную микросхему К155ИЕ8, представляющую собой двоичный делитель частоты с переменным коэффициентом деления (рис. 15, а). Такой делитель состоит из двоичного шестиразрядного счетчика VI с параллельным переносом и формирователей весовых значений частотных составляющих V4. Схема работает следующим образом. Двоичный счетчик VI непрерывно заполняется импульсами входной частоты /вх- Сигналы с прямых и инверсных выходов триггеров, входящих в состав счетчика, а также импульсы входной частоты поступают на входы формирователей V4, представляющие  Ьпппппппппппппппппппппппг , П п п п п п п п п п п п п П гп 1-1 г- гп г-1 гп . t I-1 г-i I-1 - t -1 1пппппппппппп fLn D П П п п Рис. 15. Структурная схема (й) и временные диаграммы (б) дво-ичмого делителя частоты К155ИЕ8 обой схемы И, количество которых равно количеству триггеров счетчика VI. На входы схемы И каждого разряда поступают сигналы с инверсного выхода триггера этого разря-g и прямых выходов триггеров всех предыдущих разрядов. Такая комбинация сигналов приводит к тому, что на выходе каждого формирователя появляются только те импульсы входной частоты /вх, которые переводят триггер соответствующего разряда из нулевого состояния в единичное (рйС. 15, б). Из временной диаграммы видно, что импульсы да выходе формирователей не совпадают между собой во времени. Это позволяет суммировать их на выходной схеме ИЛИ в любых сочетаниях. Управление выходной частотой производится двоичным кодом, поступающим на входы XI...Х6. Элемент V5 предназначен для последовательного соединения нескольких делителей. Предусмотрены также входы: R - установки нуля; Х7 - стробирующий; С - разрешение счета; Т - счетный. Элемент V3 формирует импульс переноса при переполнении счетчика делителя. Выходная частота снимается с выхода L3 и определяется по формуле /вых = /вхЛ^/64, где М = Х^ 2° -\- Х^ х X F -Ь . 22 + X, . 2 + X, . 2* + 2 Xi...Xe-значения двоичного кода на входах XI...Хб. С помощью делителя частоты К155ИЕ8 можно реализовать режим последовательного деления частоты на число, превышающее 64. Схема соединения микросхем в режиме деления частоты на 64 показана на рис. 16. Результирующая частота снимается с выхода L2 микросхемы D3 и определяется по формуле /вых = /бхЛ4/64, где М = (Xi)3 . 2 -f (Х,)з . 21 + (Хз)з 2 + (Х,)з 2 -f {Х,) X X 2* -Ь (Хе)з 2Ь + (Xi), . 2* + (X,), Т + (Х,), 2 -f + (Х,\ . 2 + (X,), . 2 + (Хе), . 211 + х,\ 2 -f- {Х,\ X X 2 + (Хз)1 21* -f (X,)i 2 + (Xg)! . 2i + (X )i 2 , где {1)3 ... (Хе)з, (Xi)2 ... (Хе)2, (ХЛ ... (ХЛ-значения двоичного кода на входах микросхем соответственно D3, D2, D1. fsx ~ и -Ш~\13

Рис. 16. Схема соединения при делении частоты на 64=

м и \±1 -о 1.6 1 1-5 6 о 6 - 6 XfX2XZX4 Рис. 17. Структурная схема (а) и временные диаграммы (б) в двоично-десятичных УДЧ коэффициенты вводятся в песятичном коде через логическую схему, представляющую обой преобразователь десятичного кода в двоично-десятич-рь1Й. При определенном выборе входной частоты УДЧ коэффициент деления выражается непосредственно в единицах регулируемой величины. Процесс набора требуемой частоты сводится к формированию из входной частоты /о в соответствии с задающим кодом Л^з последовательности импульсов, определенным образом распределенных в постоянном временном интервале 7 = Л о, гдеЛ - постоянная, зависящая отмаксималь-НОЙ емкости делителя, при двоично-десятичной декаде у4 = 10; /о - входная опорная частота. /л 1< 1 2 L1 L2 и и двоично-десятичного делителя частоты Таким образом, fux = NJo/lO. Структурная схема двоично-десятичного УДЧ показана на рис. 17. Двоично-десятичный УДЧ состоит из двоично-десятичного счетчика D1, работающего в коде 8-4-2-1, и формирователей весовых значений частотных составляющих D2...D5. Так держать С<РК /у Г УГЧ L- НГ Т PC ровка I dBoffl 14А>Б Л'Б сек БДЧ т Рис. 18. Структурна схема ЧЗУ Рабата схемы десятичного УДЧ аналогична работе описанного двоичного делителя частоты с той разницей, что комбинация логических сигналов на входах формирователей выбрана таким образом, что относительные значения частотных составляющих на выходах L1...L4 совпадают с весами двоичных разрядов в преобразуемом двоично-десятичном коде 8-4-2-1 (рис. 17, б). Суммирование выходных частот производится элементом D6. в качестве счетчика можно использовать микросхему j(l55HE6. Управляющий код поступает на входы XI... Х4. Импульс переполнения счетчика снимается с выхода L6. Построение УДЧ с коэффициентом деления больше десяти выполняется последовательным соединением нескольких десятичных УДЧ. В этом случае импульсы переполнения предыдущей декады являются входными импульсами преобразуемой частоты для следующей декады. Код задания Л^з зависит от способа задания программы, типа датчика, применяемого в цепи обратной связи системы, а также от специальных требований, предъявляемых к задающим устройствам, и может формироваться с помощью механических переключателей или цифровыми логическими устройствами. При формировании кода с помощью переключателей существенно упрощается устройство ввода и облегчается контроль за набором задающего кода, так как численное значение кода задания однозначно определяется положением переключателей. Однако при изменении кода задания во время работы устройства в момент переключения выходные импульсы пропадают, особенно при изменении в старших разрядах, которое обусловлено конечной длиной межконтактного промежутка переключателя. Кроме того, при таком построении устройства ввода задания нельзя автоматически управлять режимами работы ЧЗУ. При формировании кода с помощью цифровых устройств (реверсивные счетчики, сумматоры, регистры памяти) эти недостатки устраняются. Структурная схема разработанного авторами частотного задающего устройства для цифроаналоговой системы управления частотой вращения двигателя постоянного тока изображена на рис. 18. С помощью устройства можно управлять режимами работы двигателя, в том числе: 1. Производить разгон и торможение двигателя с заданным ускорением (замедлением) до требуемой частоты вращения с фиксированием любой промежуточной частоты вращения при разгоне (торможении) по команде Так держать, 2. Осуществлять ручную коррекцию частоты вращения двигателя в небольших пределах по командам оператора. 3. При любой коррекции частоты вращения двигателя в том числе и останове, его устройство сохраняет предвари! тельно набранное значение рабочей частоты вращения. В ЧЗУ входят кварцевый генератор КГ, двоично-деся-тичный УДЧ, реверсивный счетчик PC, управляемый генератор УГЧ, низкочастотный генератор НГ, схема формирования команд управления СФК, схема сравнения кодов ССК, буферный делитель частоты БДЧ, схема ввода и хранения кода задания СВЗ, устройство индикации ЦИ. Выходную частоту устройства можно представить как п сумму импульсов каждой декады УДЧ: /вых = ifo/0\ где /вьж - выходная частота; i - номер разряда вводимого десятичного числа; Ni - значение коэффициента деления в г-м разряде; п - количество разрядов вводимого числа. Диапазон изменения частоты вращения электродвигателя 0...999 мин- с дискретностью в 1 мин-. Следовательно, для обеспечения требуемого диапазона необходимо иметь три последовательно соединенные декады УДЧ с коэффициентом деления, равным 1000. Выходная частота формируется из последовательности импульсов кварцевого генератора /о и поступает в буферный делитель БДЧ. Управление УДЧ производится трехдекадньш двоично-десятичным реверсивным счетчиком PC, причем старшая декада PC управляет работой младшей декады УДЧ. Управление режимами PC и определение моментов достижения заданной частоты вращения производятся узлом сек, сравнивающим код задания с текущим, вырабатываемым в PC. Схема формирования команд СФК предназначена для выработки логических сигналов, управляющих работой устройства. 1 ... 3 4 5 6 7 8 9 ... 16 |

|

© 2000-2026. Поддержка сайта: +7 495 7950139 добавочный 133270.

Заимствование текстов разрешено при условии цитирования. |