|

|

|

|

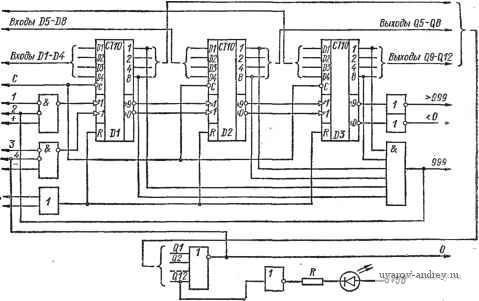

Главная страница » Электрика в театре » Схемы с частотным преобразованием 1 2 3 4 5 6 7 ... 16 Входы Ъ9-Ш Вшсды ufQ4  Рис. 6. Схема двоично-десятичного счетчика чики не поступают. Счетные импульсы можно подавать одновременно на входы + и - , а направлением счета управлять сигналами на входах 1 я 3. Счет в направлении + происходит до тех пор, пока число, записанное в счетчике, меньше 999. Когда это число становится равным 999, на выходе > 999 появляется логическая единица, запрещающая дальнейшее поступление импульсов. Аналогично на выходе < О появляется сигнал 1 , когда число, записанное в счетчик, равно нулю, который запрещает дальнейшее поступление импульсов по входу - . Допускается соединение двух ячеек РС-4 для получения счетчика емкостью 10~*-1. Для этого выходы <; 999 и <С О первой ячейки подаются соответственно на входы + и - второй, а выходы > 999 и -< О второй соединяются с одноименными выходами первой (выходы выполнены по схеме с открытым коллектором, при этом допускается такое прямое соединение). В схеме ячейки предусмотрена возможность предварительной установки счетчиков в любое состояние. Код этого состояния подается на входы D1...D 12; при подаче сигнала О на вход С этот код переписывается в счетчик и появляется на выходах 1...12 независимо от счетных импульсов. При подаче сигнала 1 на вход сброса счетчики переходят в нулевое состояние. Состояние выходов счетчика индицируется светодиодами, установленными на лицевой панели ячейки. В цифровых и цифроаналоговых САУ счетчики подобных типов широко используются для подсчета числа импульсов за заданное время в преобразователях частота - код, Б качестве элемента сравнения, интегратора разности частот и т. д. В ячейке реверсивного счетчика РС-5 содержится 6 микросхем К155ИЕ6, соединенных по схеме двух реверсивных счетчиков, емкостью 999. Выходы всех разрядов счетчиков выведены на внешний разъем, однако предварительная установка счетчиков не предусмотрена. Эта ячейка исполь- зуется в цифровом интеграторе и цифровом широтно-импульсном модуляторе. Три микросхемы К155ИЕ8 в ячейке управляемого делителя частоты УД-1 могут работать либо в режиме управляемого шестиразрядным кодом делителя частоты на 2, либо при их последовательном соединении в режиме управляемого 12- или 18-разрядным кодом делителя частоты соответственно на 2 или 2. Операции 6 кодами в цифровых САУ выполняются проще при использовании двоичных кодов. В то же время ввод уставок и вывод параметров на индикацию проще осуществляется в двоично-десятичном коде. В связи с этим возникает необходимость в преобразователях двоично-десятичного кода в двоичный и обратно. Ячейка ПК-1 выполняет преобразование кодов двух чисел, максимальные значения которых равны 999 и 99, из двоично-десятичных в двоичные. Предусмотрена возможность совместной работы двух таких ячеек для преобразования кода числа с максимальным значением 9999. С помощью ячейки ПК-2 выполняется преобразование двоичного кода числа, максимальное значение которого равно 4095, в двоично-десятичный. В цифровых и цифроаналоговых САУ часто возникает необходимость в перемножении двух чисел, заданных двоичными кодами, например, при формировании кодов или частот задающих сигналов, при вычислении различного рода составляющих закона регулирования [15] и др. Ячейка УК-1 является устройством умножения матричного типа. Умножение двоичных чисел, имеющих п цифр множимого и т множителя, сводится к последовательному сдвигу множимого на 1, 2, 3, ... разрядов и суммированию полученных чисел, причем, если в /-м разряде множителя стоит нуль, то сдвинутое на i разрядов число заменяется нулем. Устройство умножения матричного типа формирует сдвинутые числа множимого и суммирует их с учетом соответствующей цифры множителя. Предусматривается возможность совместной работы нескольких таких ячеек. С помощью одной ячейки можно перемножать коды чисел при п = 4 и /п = 6, двух ячеек - п = 8ит = 6 или п = 4 и m = = 11, четырех -п = 8 и m == 11, шести - п = 12 и m = 11 или п = 8 и m = 16 и т. д. Устройство умножения матричного типа является быстродействующим и помехоустойчивым, так как не содержит элементов памяти. Однако в нем много микросхем, поэтому оно громоздко и потребляет большую мощность. Было разработано сдвиговое устройство умножения УК-2, в котором поочередно выполняются операции сдвига множимого и суммирования полученного числа с ранее сформированной частичной суммой. В ячейке УК-2 суммирование выполняется с помощью микросхемы К155ИМЗ, сдвиг и запоминание результатов суммирования - с помощью микросхемы К155ИР13. Необходимая последовательность работы (запись результата очередного суммирования при наличии единицы в данном разряде множителя, сдвиг, запись и т. д.) обеспечивается с помощью логической схемы и распределителя импульсов, выполненного на микросхеме четырехразрядного счетчика и микросхеме К155ИДЗ. Ячейка УК-2 выполняет умножение кодов при п - т = 8 за время 24 МКС. Предусмотрена возможность совместной работы двух таких ячеек для умножения кодов при п = т = 16. Запоминающий регистр ЗР-1 предназначен для запоминания четырех четырехразрядных кодов, поступающих на вход ЗР. При подаче импульсного сигнала на тактирующие входы входная информация появляется на выходе ЗР. Запоминание информации производится с помощью микросхемы К155ТМ7. Предусмотрена световая индикация введенных кодов с помощью светодиодов, установленных на лицевой панели ячейки. Запоминающий регистр ЗР-1 используется для ввода сигналов задания (например, если одна ЦВМ выдает уставки последовательно нескольким САУ), для запоминания результатов вычислений на время машинного такта (фиксатор), для вывода информации и др. Ячейка селектора СЕ-1 обеспечивает выбор одного из Код R R R ГЦ 2П  2R K2 2R КЗ Рис. 7. Схема ПКН вьа вых четырех поданных на ее информационные входы кодов в зависимости от кодовой комбинации на управляющих входах. С помощью одной ячейки происходит селекция шестиразрядного кода. Основой ячейки является микросхема К155КП2. Эта ячейка используется в цепях задания, когда в зависимости от режима работы объекта на вход его САУ нужно подать заранее зафиксированный код, а также в тех случаях, когда одна САУ обслуживает несколько объектов управления и в нее нужно ввести сигналы с объекта, обслуживаемого в данный момент. Для согласования цифровой и аналоговой частей САУ применяется ячейка преобразователя код - напряжение (рис. 7), которая предназначена для преобразования числа в двоичном или двоично-десятичном коде в пропорциональное этому числу напряжение постоянного тока. В состав ПКН входят две декодирующие интегральные резисторные матрицы, построенные по принципу R - 27?, восемь двух-позиционных ключей К1...К8, построенных на интегральных полевых коммутаторах и транзисторных матрицах, выходной усилитель А1 с инвертором А2, предназначенные для согласования выходного сопротивления преобразователя с сопротивлением нагрузки, установки требуемого масштаба выходного напряжения и получения двух парафазных выходных сигналов. Кроме того, в преобразователе имеется бесконтактное реле БР с двумя взаимно инверсными ключами, которое используется в тех случаях, когда требуется изменить полярности выходного сигнала по команде от управляющего сигнала Иупр. Преобразуемый код подается на входы ключей К1...К8. Выходное напряжение снимается либо с выхода усилителя А1, либо с выхода инвертора А2 (противоположной полярности), либо с выхода бесконтактного реле БР (знакопеременное). Преобразователь код - напряжение предназначен для работы в двух режимах: преобразование входного кода (восемь разрядов двоичного или две тетрады двоично-десятичного) в пропорциональное накряжение постоянного тока и умножение входного напряжения, подаваемого вместо Ыэт> на число, заданное в двоичном или двоично-десятичном коде с той же разрядностью. Для децентрализованного питания описанных выше устройств разработан источник питания, представляющий собой плату размерами 100 х 160 мм с шириной лицевой панели 45 мм. Источник обеспечивает ток нагрузки 4 А при выходном напряжении 5 В. Генераторы тактовых импульсов и схемы синхронизации. Одними из наиболее распространенных узлов частотных цифроаналоговых САУ являются генераторы тактовых импульсов (ГТИ), вырабатьшающие импульсные последовательности, необходимые для работы узлов задания цифрового корректора, измерителя скорости и других, и схемы синхронизации (СС), осуществляющие преобразование произвольно поступающих импульсов в последовательность импульсов тех же частот, но жестко сфазированных относительно импульсов ГТИ. Чаще применяются следующие два типа ГТИ. В устройствах, работа которых не определяется высокой стабильностью тактовой частоты, используются ГТИ, представляющие собой релаксационные генераторы с времязадающими 7?С-цепями. В узлах задания скорости, формирователях временных интервалов цифровых измерителей скорости и соотношения скоростей используются кварцевые генераторы, позволяющие получать последовательности импульсов высокой точности и стабильности. Схема ГТИ, вырабатывающего две тактовые последовательности с фазовым сдвигом в 180 , показана на рис. 8, а. Он выполнен по схеме мультивибратора с емкости ными связями (С/, С2) на интегральных микросхемах серии К155 (D1 и D2). Автоколебательный режим работы схемы обеспечивается подачей напряжения смещения на выходы инверторов через резисторы R1 и R2 непосредственно с выходов этих инверторов (отрицательная обратная связь по постоянному току). Выходное напряжение инверторов С2 ИЗ R2 V: Fr С4 1 . Рис. 8. Схемы ГТИ: а - релаксационного; б - с кварцевым резонатором поступает в противофазе на дифференцирующие цепочки R3C3 и R4C4, которые формируют короткие импульсы, совпадающие с передним (первый канал) и задним (второй канал) фронтами импульсной последовательности. Таким образом, на выходе дифференцирующих цепочек образуются две последовательности импульсов (Fi и Fis), сдвинутых друг относительно друга на 180 . При построении кварцевых генераторов на интегральных логических схемах используются линейные участки характеристики интегральных схем. Схема генератора, построенная на микросхемах серии К155, показана на рис. 8, б. Резисторы R1 и R2 служат для смещения рабочих точек элементов D/ и D2 в линейную область, конденсатор С1 - для развязки элементов по постоянному току. С помощью конденсаторов С2 и СЗ можно изменять частоту генерации в небольших пределах. Формирование выходных импульсов осуществляется элементом D3. Генератор устойчиво работает на частотах 1...5 МГц при отклонении частоты генерации от номинальной частоты кварцевого резонатора на ±5 10~%. При сложении или вычитании двух или нескольких последовательностей импульсов может происходить наложение импульсов, когда временной интервал между некоторыми импульсами двух частот меньше времени срабатывания логических элементов или равен нулю. В этом случае возможны сбои в работе цифровых устройств (например, при одновременном поступлении импульсов на оба входа 7?5-триггера) или потеря информации (если импульсы одновременно поступают на счетный вход триггера). ! Входные импульсы благодаря схеме синхронизации поступают в дискретные устройства в строго определенные моменты времени. Каждый импульс входной последовательности запоминается схемой синхронизации и появляется на ее выходе только в момент прихода импульса тактовой частоты f. Количество тактовых частот равно числу синхронизируемых импульсных последовательностей. Рис. 9. Двухтактная схема синхронизации (а) и ее временные диаграммы (б) Схема синхронизации, выполненная на элементах серии К155, изображена на рис. 9, а. Она содержит два D-триггера D1 а D2 и схему совпадения D3. В исходном состоянии оба триггера находятся в нулевом состоянии. На входе D-триггера DI присут твует постоянный единичный сигнал, поэтому при появлении входного 1 2 3 4 5 6 7 ... 16 |

|

© 2000-2026. Поддержка сайта: +7 495 7950139 добавочный 133270.

Заимствование текстов разрешено при условии цитирования. |